Chinese Academy of Sciences released the domestic RISC-V processor "Xiangshan" Has successfully run Linux in July

Xiaocha from the concave temple

Qubit Report | Public Account QbitAI

This week, the first RISC-V China Summit was held at ShanghaiTech University. This is the first time that RISC-V has held a summit of the same scale outside of North America.

At this conference, Bao Yungang , a professor at the University of Chinese Academy of Sciences and a researcher at the Institute of Computing Technology of the Chinese Academy of Sciences, announced the core of the domestic open source high-performance RISC-V processor- Xiangshan .

Speaking of why the "fragrant mountain" should be built, Bao Yungang said that an open source RISC-V core core like Linux should be established, which can be widely used in the industry and support the academia to experiment with innovative ideas.

And let it survive at least 30 years like Linux!

(Note: The following Xiangshan technical materials have been authorized by Teacher Bao Yungang.)

01 R&D history

After more than a year of preparation, on June 11, 2020, Xiangshan established a code repository on GitHub.

Afterwards, Xiangshan's research and development progressed very fast: on July 6th, the out-of-order pipeline was completed and CoreMark was able to run correctly; on September 12th, Linux started correctly; on October 22nd, Debian started correctly.

In just one year, 25 students and teachers participated in the development of Xiangshan and submitted more than 50,000 lines of code.

The core of Xiangshan is named after the "lake" structure code. The first generation is called "Yanqi Lake", which means it came from the University of Chinese Academy of Sciences.

The "Yanqi Lake" RTL code was completed in April this year, and it is planned to be taped out in July based on TSMC's 28nm process.

The second-generation architecture is called "Nanhu" and will use SMIC's 14nm process. It is expected to be taped out by the end of this year.

Xiangshan processors not only have scientific research institutes, but also enterprises. Among them, Beijing Microcore participated in the first phase of the design work.

The team is currently recruiting Xiangshan processors for the second phase of joint development partners, and the companies that have joined include ByteDance and other companies.

So, what is the actual performance of these two chips?

02 Performance parameters

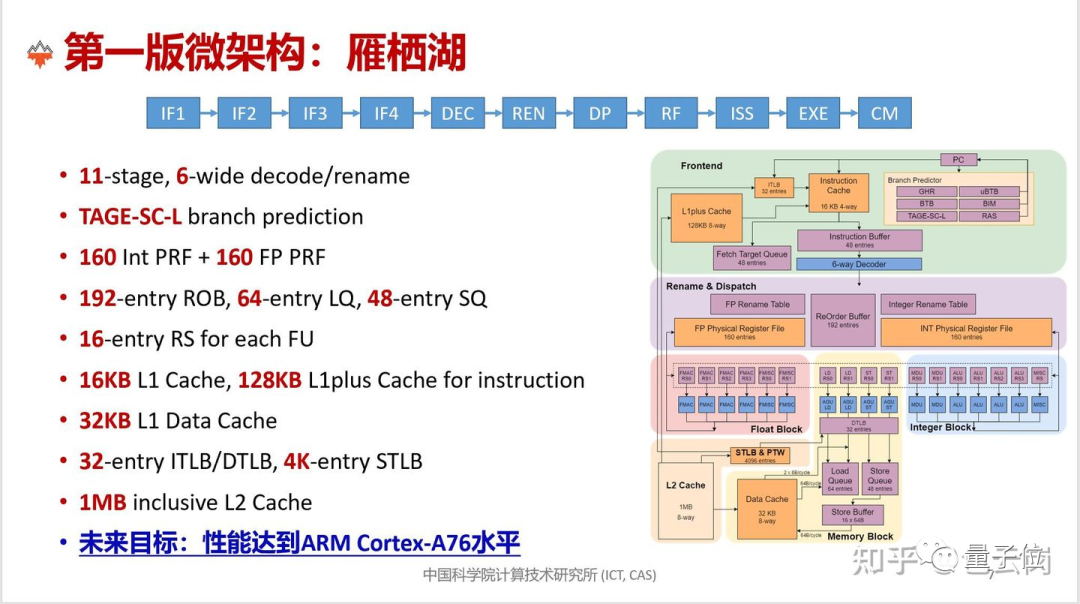

"Yanqi Lake" adopts out-of-order execution, 11-level flow, and 6-launch. Due to the use of the older 28nm TSMC process, the main frequency is low and is expected to reach 1.3Ghz.

The performance score of "Yanqi Lake" SEPC2006 is about 7/Ghz. From this point of view, the first-generation architecture of Xiangshan mainly targets ARM's A72 or A73.

The second-generation architecture has greatly improved performance. Bao Yungang said that the goal of "Nanhu" is to reach 20 points for SEPC2006, which is 10/Ghz, which is close to the 11.08/GHz of i9-10900K.

The team hopes that in the future, through continuous iterative optimization ("South Lake"→"X Lake"→"Y Lake"→……), the performance of "Xiangshan" will reach the level of ARM A76.

It is worth mentioning that today RISC-V chip manufacturers have launched the world’s fastest RISC-V CPU-P550. The actual performance of this chip is 8.65/Ghz (SPECInt 2006), against the standard ARM A75.

P550 will use Intel's 7nm technology, and Intel 7nm will not be available to the market until at least 2023, so this chip will not be available in the short term.

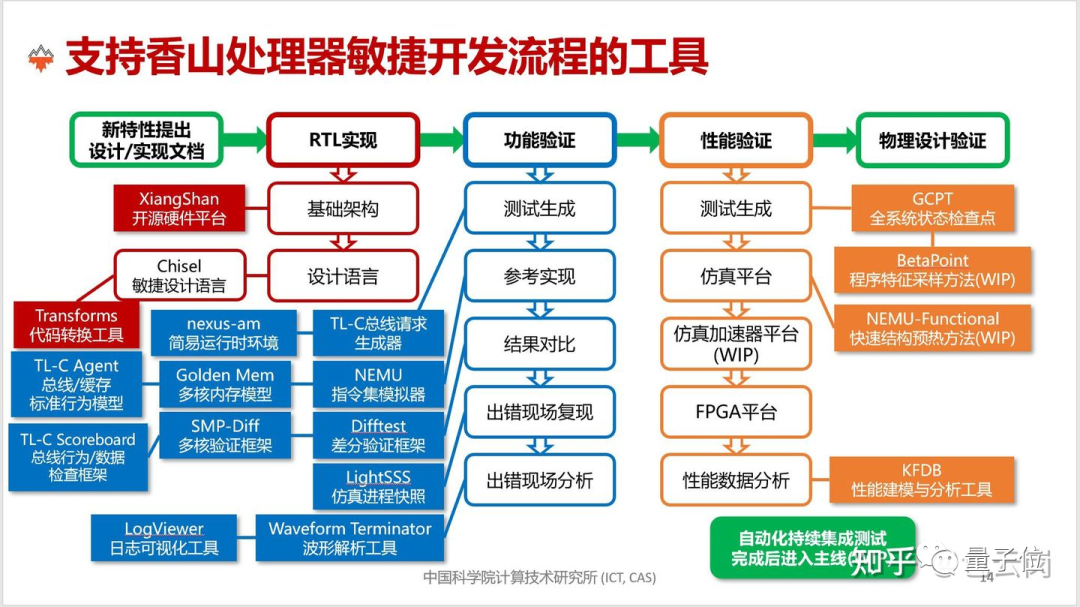

In order to develop such a chip, Bao Yungang's team also developed a series of processes, platforms, and infrastructure. For example, in order to better support Chisel development and debugging, the team has developed more than ten tools to support a set of agile development process of processor chips.

According to the submissions, this RISC-V China Summit will add "Xiangshan Session" to the Xiangshan RISC-V processor of the Institute of Computing Technology of the Chinese Academy of Sciences on the basis of the existing classification, and receive 12 reports from the Xiangshan processor.

On the afternoon of June 25th, Xiangshan will hold an online tutorial to introduce Xiangshan's development tool chain, simulation debugging tools, etc. Developers interested in processor design can sign up.

COMMENTS